JK触发器可以形成d触发器和t触发器。根据逻辑功能,触发器可分为rs触发器、JK触发器、D触发器和T触发器,JK触发器可以用来构成D触发器和T触发器,D触发器是上升沿还是下降沿,说明了D触发器和由JK触发器组成的T触发器的区别,1.大多数D触发器由上升沿触发,而JK触发器由下降沿触发。当它们连接成T触发器时,只是触发方式不同。

1、d触发器是上升沿还是下降沿

解释一下D触发器和JK触发器组成的T触发器的区别。1.大多数D触发器由上升沿触发,而JK触发器由下降沿触发。当它们连接成T触发器时,只是触发方式不同。2.JK触发器通用性强,可以灵活转换成其他类型的触发器。JK触发器可以用来构成D触发器和T触发器。d触发器有两种触发方式:电平触发和边沿触发。前者可以在CP(时钟脉冲)1触发,后者在CP前沿触发(正跃迁0→1)。

JK触发器可以形成d触发器和t触发器。d触发器有两种触发模式:电平触发和边沿触发。前者可在CP(时钟脉冲)等于1时触发,后者主要在CP(正跳0→1)前触发。4.逻辑功能的区别:当JK触发器具有时钟脉冲功能时,当J和K都为0时,状态不变;当j为0,k为1时,二级状态为0;当j为1,k为0时,二级状态为1;当J1K1时,二次状态与当前状态相反。

2、JK触发器的产品分类

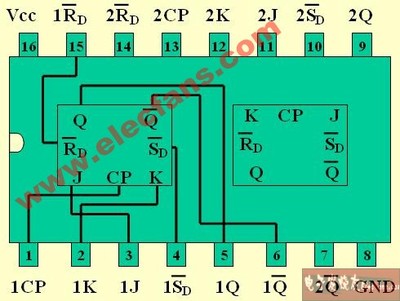

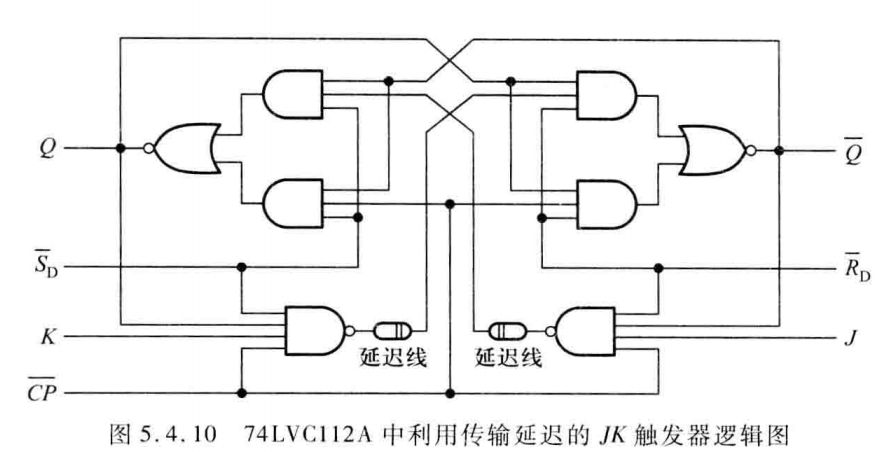

电路结构主从JK触发器由主从RS触发器组成,如图7.5.1所示。在主从RS触发器的R端和S端分别增加两个输入与门G11和G10,Q端和输入端输出为原S端,输入端称为J端,Q端和输入端输出为原R端,输入端称为K端。工作原理SJQ和RKQ可以从上面的电路中得到。代入主从RS触发器的特性方程,我们得到:当J1,K0,Qn11J0,K1,qn10JK0,qn1qnJK1,Qn 1 ~ Qn;从上面的分析来看,主从JK触发器是没有约束的。

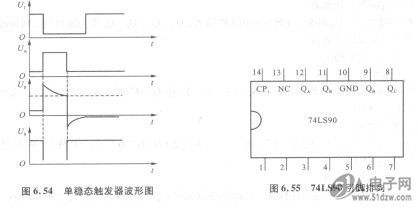

每次输入时钟脉冲时,触发器翻转。触发器的这种工作状态称为计数状态,输入时钟脉冲的个数可以通过触发器工作特性建立时间的个数来计算:指输入信号应先于CP信号到达的时间,用tset表示。从图7.5.5可以看出,J和K信号只需要不晚于CP信号到达,所以有tset0。保持时间:为了保证触发器的可靠翻转,输入信号需要保持一定的时间。

3、主从型JK触发器

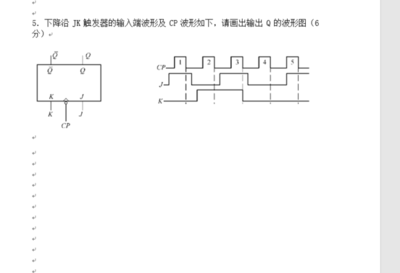

CP上下波动,对J和k没有影响,第一个触发器JA,K1,第二个触发器J1,K1都是固定的,会变化,是Q1和Q2的值。我画了变化波形。我大概知道我误解了什么,因为Q1是在CP从1变到0之后才变的(我画了一条虚线来延伸),所以第二个CP脉冲起作用,也就是说CP2从1变到0之后,Q1是0,Q2是1。我画的还是很清楚的。请你自己看。

j是1,K是1,而1,Qn是0。根据特征方程,Q1等于1,Q1不等于0。两个JK触发器不起作用。当cp第二次从1变为0时;j是0,k是1,Qn是1。根据特征方程,Q1等于0,Q1不等于1。当第二个触发器不起作用时,第三个cp从1变为0;a是1,k是1,Qn是0。Q11由特征方程得到,Q1不等于0。第二个JK触发器的状态J为1,k为1Q2,a选自特征方程Q2。

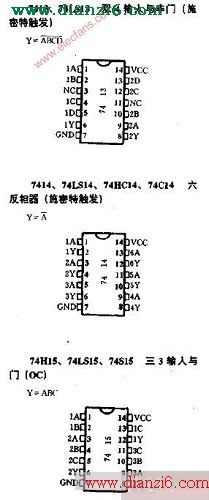

4、触发器的类型及应用基本RS触发器JK触发器的逻辑电路及逻辑功能

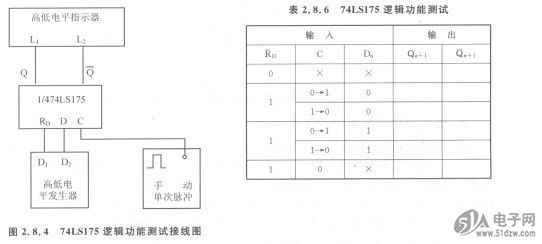

(1)触发器是一种可以存储1位二进制代码的逻辑电路,是时序逻辑电路的基本单元。触发器的种类很多,分类方法也不一样。根据逻辑功能,触发器可分为rs触发器、JK触发器、D触发器和T触发器。RS触发器有RS = 0的约束条件,D触发器和T触发器的功能相对简单,JK触发器的逻辑功能最灵活。

它们以不同的方式被触发。基本RS触发属于电平触发,同步触发和主从触发属于脉冲触发,边沿触发是脉冲边沿触发,可以是上升沿触发,也可以是下降沿触发。只有了解这些不同的动作特征,才能正确使用这些触发器。特别需要指出的是,触发器的电路结构和逻辑功能是两个完全不同的概念,两者之间没有固定的对应关系。相同逻辑功能的触发器可以用不同的电路结构实现;相同电路结构的触发器可以做成不同的逻辑功能。

5、如何用JK触发器设计计数器

3)通过计数增减点数:加法计数器、减法计数器、加减计数器. 7.3.1异步计数器1、异步二进制计数器1、异步二进制加法计数器分析图7.3.1由JK触发器组成的4位异步二进制加法计数器。分析方法:从逻辑图到波形图(所有JK触发器都是T/触发器的形式)

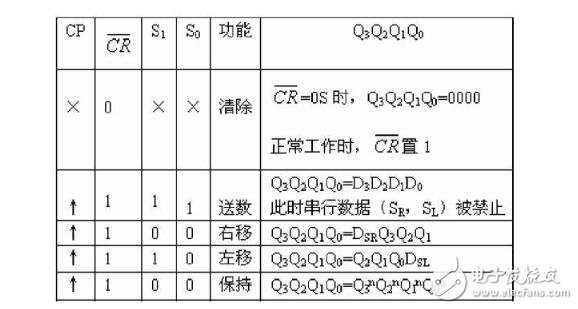

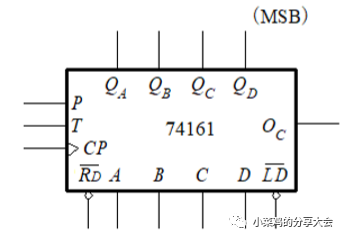

异步二进制减法计数器的减法规则:00001可以看作是(1);10等等。注:74LS163的引脚排列与74LS161相同,不同的是74LS163采用同步清零模式。(2)2)CT 74ls 161的逻辑功能是10点钟异步清零。C0021,0点同步平行设置。(3)使用CPT CPP01时,按照4位自然二进制码进行同步二进制计数。

6、jk触发器的逻辑功能是

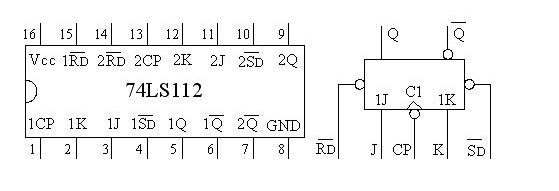

JK触发器和D触发器现在处于正常逻辑功能时,sd\\\\rd应该处于什么状态?当符号上有非符号时,信号低电平有效,无非符号时,信号高电平有效。使用时,始终使触发器set end无效。触发器可以正常使用。其他信号可以施加到这两个端子来控制触发器。计数器中的级联就是这种方法。逻辑功能的区别:当JK触发器有时钟脉冲动作时,当J和K都为0时,状态不变;当j为0,k为1时,二级状态为0;当j为1,k为0时,二次态为1;当J1K1时,二次状态与当前状态相反。

如果输入端有一个圆圈,表示低电平驱动。当SD或RD端有驱动信号时,触发器的状态不受时钟脉冲和控制输入端状态的影响。逻辑功能上的区别:当JK触发器有时钟脉冲效应时,当J和K都为0时,状态不变;当j为0,k为1时,二级状态为0;当j为1,k为0时,二级状态为1;当J1K1时,二次状态与当前状态相反。低水平是有效的。

7、jk触发器工作的原理是什么

JK触发器的工作原理可以概括为:1。当有效时钟的脉冲沿没有到达,即clk0、clk1或clk从高电平跳到低电平时,与非门G3和G4屏蔽J和K端的输入信号,触发器的状态保持不变,不受输入信号的影响,2.当时钟上升沿信号到来时,触发器的状态会随着J和K的输入而相应变化..具体来说,当J0和K0时,触发器的状态保持不变,即QnQn 1。